薄膜晶体管(TFT,Thin⁃film Transistor)是集成电路领域中一种重要的基础性电子器件,本质为场效应晶体管[1].高性能、低功耗和小的特征尺寸一直都是集成电路发展的必然趋势,为获得更高性能和更小尺寸的TFT,选择合适的有源区材料和栅介质层材料至关重要.通常半导体纳米薄膜具有很好的机械、电学和光学性能,其中硅纳米薄膜是一种与传统的互补金属氧化物半导体(CMOS)工艺相互兼容且制备简单,成本较低的材料,适于制作多种电子器件,如TFT[2,3],PIN二极管和光电探测器等.有的课题组在晶向为111和001的硅基底上通过分子束外延的方法生长厚度仅为4 nm的GeSn作为栅介质层,成功实现了具有室温下最低可实现的亚阈值摆幅和较高的电流开关比的隧穿场效应晶体管[4].对于TFT而言,基于传统栅介质材料SiO2的TFT(STFT)很容易被击穿.为了改善晶体管的性能,需要探索高介电常数(高k)的材料,其中基于高k材料ZrO2作为栅介质层的具有高的空穴迁移率,并且电容等效厚度在1 nm以下的高性能GeP型MOSFET已经被成功制作[5],除此之外,HfO2也是一种介电常数较高、带隙较宽的栅介质层材料,基于该材料也实现了高性能的薄膜晶体管[6].通过建模仿真的方法将HfO2作为栅介质层的TFT(HTFT)的性能与STFT进行对比,证明了高k材料对于实现更高性能的晶体管具有重要的意义.

为了确定设计晶体管的结构和所选择材料的合理性,利用Sentaurus软件对器件进行建模和性能研究,从而判断是否达到预期的目标以及适当调整相关的参数,对性能进行优化,为后续的工艺制作打下基础.目前基于该软件实现了多种晶体管的建模 [7,8,9,10,11],实现了P阱绝缘体上硅场效应晶体管的建模[12],研究器件在辐照的条件和应变条件下表现出的性能变化[13,14,15,16,17],掺杂剂量和沟道长度对于晶体管性能的影响等[18,19].但是利用该软件进行高k材料TFT的建模并系统地研究沟道长度和宽度、栅介质层的厚度和材料对于TFT性能的影响的研究还很有限.通过将STFT和HTFT进行建模和性能的研究与对比,发现HTFT具有更高的电流开关比和更小的阈值电压和漏电流,验证了使用高k材料的TFT具有更好的开关特性,更高的驱动能力和频率响应,对于尺寸更小,集成度更高的集成电路具有重要意义.

1 薄膜晶体管的结构设计与建模

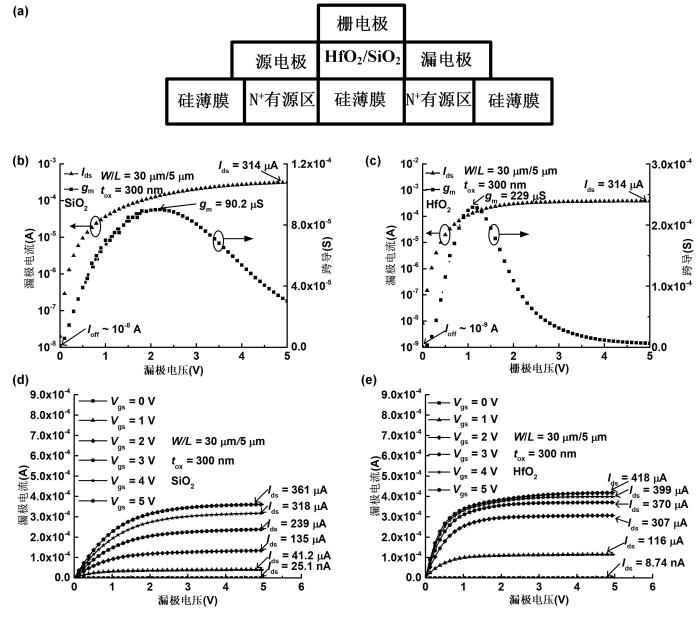

所设计的TFT的结构是顶栅结构,硅纳米薄膜被选择作为有源区的材料,可以实现较高的载流子迁移率,因而可以获得开关特性更好的薄膜晶体管.栅介质层材料选择的是传统的SiO2和高k材料HfO2,源漏栅金属电极的材料均为金.对STFT和HTFT在沟道长度(L)、沟道宽度(W)和栅介质层厚度(tox)分别为 5 µm,30 µm和300 nm,温度(T)为300 K时转移特性曲线和输入输出特性曲线(I⁃V特性)进行了表征,最终的结构图和性能曲线图如图1所示.

图1

从转移特性中可以看出,STFT在关态下的漏电流Ioff约为10-8 A,而HTFT在关态下的漏电流Ioff接近10-9 A,TFT的开关比即为TFT的开启电流与关态漏电流的比值.由此可以得到STFT的开关比大约为1.5×104,而HTFT的开关比为4×104,说明硅基薄膜晶体管具有较好的工作特性,同时也说明基于高k栅材料的TFT具有更高的开关比和更小的关态漏电流,即相比传统的基于SiO2的TFT有更好的工作性能.从转移特性中也可以得到TFT的阈值电压(Vth),STFT和HTFT相对应的Vth分别为0.69 V和0.52 V,说明HTFT的栅极相对于STFT具有更强的驱动能力.从图中同样可以得到器件的亚阈值摆幅(SS),反映晶体管的亚阈区特性,在数量上可以用下式表示:

SS对于STFT和HTFT分别为90 mV·dec-1和80 mV·dec-1,说明HTFT比传统的STFT在亚阈值区有更高的频率响应.从转移特性图也可以得到TFT的跨导值,跨导可以用式(2)计算:

即跨导在数学上为源漏电流随栅电压的变化率.HTFT的最大跨导值为229 μS,而STFT的最大跨导值为90.2 μS,说明HTFT具有较高的增益.利用跨导值可以通过式(3)计算得到晶体管的有效载流子迁移率:

其中,μn是有效载流子迁移率,Vds是漏端电压,Cox是单位面积的栅电容,计算公式为:

其中,ε0是真空介电常数,为8.85×10-12 F·m-1,εr是栅介质层材料的相对介电常数,对于HfO2和SiO2分别为22和3.9.

通过计算发现,HTFT的有效载流子迁移率大约为266 cm2·V-1·s-1,而STFT的有效载流子迁移率大约为653 cm2·V-1·s-1.高介电常数的材料载流子迁移率退化主要受到声学波散射、极性光学波散射和电离库伦散射等多种散射机制的影响.

2 薄膜晶体管的性能表征

2.1 不同沟道长度TFT的性能对比 图2所示为STFT和HTFT在W和tox分别为30 µm和300 nm,T为300 K,L的值分别为3 µm,

图2

图2

不同沟道长度的TFT对应的性能曲线的对比图

Fig.2

Comparison of the performance curves of TFTs with different channel length

从图2可以看出,对于STFT,不同L对应的器件的Vth相同,均为0.69 V;对于HTFT两种沟道的器件对应的Vth也相同,为0.52 V.随着L的增加,晶体管饱和区的输出电流反而在逐渐减小,电流的开关比也在逐渐减小.晶体管工作时的电流计算公式如下:

由式(5)和式(6)可以看出,晶体管的饱和电流与L成反比,因而在W,tox和T相同的条件下,随着L的增加晶体管的饱和电流反而逐渐减小.L为3,4,5 µm的STFT的饱和电流分别为572,388,314 μA,是沟道长度为6 µm的STFT的饱和电流246 μA的2.32倍,1.58倍和1.28倍.对于HTFT,L=3,4,5 µm时对应的饱和电流分别为641,456,384 μA,是L=6 µm对应的饱和电流316 μA的2.03倍,1.44倍和1.22倍.在I⁃V特性曲线中,对于HTFT,L=3,4,5 µm时对应的饱和电流分别为549,370,306 μA,是L=6 µm对应的饱和电流274 μA的2倍,1.35倍和1.12倍,与理论计算基本一致,对于STFT也满足相应的倍数关系.这说明STFT和HTFT都有较好的工作性能,且HTFT比STFT的性能更高,体现了高k材料制作晶体管的优势.

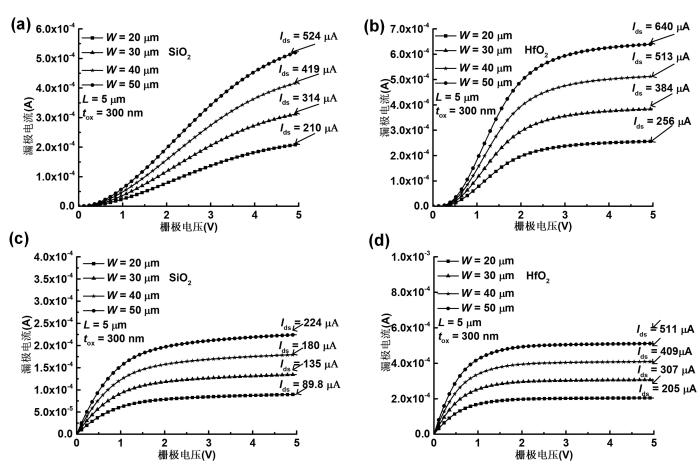

2.2 不同沟道宽度TFT的性能对比

图3

图3

不同沟道宽度的TFT对应的性能曲线的对比图

Fig.3

Comparison of the performance curves of TFTs with different channel width

由式(5)和式(6)可以看出,饱和电流与Cox成正比,Cox与晶体管沟道宽度W成正比,则饱和电流随W的增加而增加,与仿真结果一致.跨导的最大值也随着W的增加而线性增加.

在转移曲线中,沟道宽度为50,40,30 µm的STFT的饱和电流分别为524,419,314 μA,是沟道宽度为20 µm的STFT的饱和电流210 μA的2.5倍,2.0倍和1.5倍.对于HTFT也具有相同的特点,沟道宽度为50,40,30 µm的HTFT的饱和电流分别为640,513,384 μA,是沟道宽度为20 µm的HTFT的饱和电流256 μA的2.5倍,2.0倍和1.5倍,与理论的结果相一致.在输入输出特性曲线中,沟道宽度为50,40,30 µm的STFT的饱和电流分别为224,180,135 μA,是沟道宽度为20 µm的STFT的饱和电流89.8 μA的2.5倍,2.0倍和1.5倍.对于HTFT也具有相同的特点,沟道宽度为50,40,30 µm的HTFT的饱和电流分别为511,409,307 μA,是沟道宽度为20 µm的HTFT的饱和电流205 μA的2.5倍,2.0倍和1.5倍,与理论的结果相一致.这说明STFT和HTFT都具有较好的工作性能.

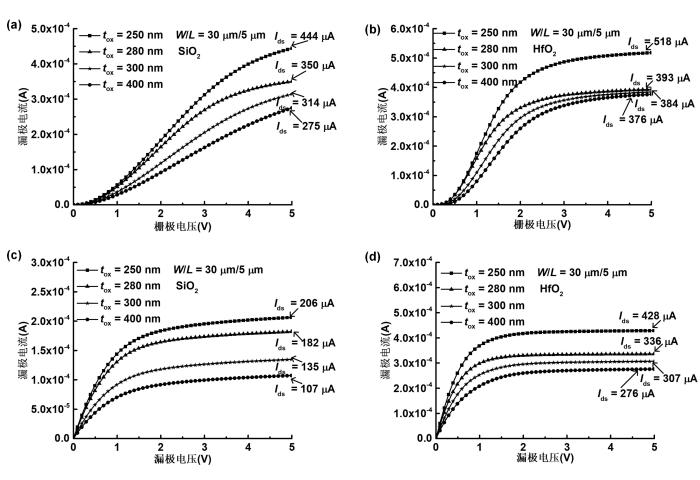

2.3 不同栅介质层厚度TFT的性能对比

图4

图4

不同栅介质层厚度的TFT对应的性能曲线的对比图

Fig.4

Comparison of the performance curves of TFTs with different gate dielectric thickness

由电流的公式可以看出,饱和电流与Cox成正比,而Cox与tox成反比,因而晶体管的饱和电流和开关比都随着tox增大而逐渐减小,与图中的性能仿真结果一致.通过对比发现,HTFT的饱和电流值和跨导值相比于同一栅介质层厚度的STFT要高,同时tox为250,280,300 nm的STFT的饱和电流分别为444,350,314 μA,是tox为400 nm的STFT的饱和电流275 μA的1.61倍,1.27倍和1.14倍.对于HTFT也具有相同的特点,tox为250,280,300 nm的HTFT的饱和电流分别为518,393,384 μA,是tox为400 nm的HTFT的饱和电流376 μA的1.38倍,1.04倍和1.02倍.在输入输出特性曲线中,tox为250,280,300 nm的HTFT的饱和电流分别为428,336,307 μA,是tox为400 nm的HTFT的饱和电流276 μA的1.55倍,1.22倍和1.11倍,与理论计算结果也几乎一致,对于STFT也满足相应的倍数关系.这也说明STFT和HTFT具有晶体管的正常性能,且由于HTFT相对STFT具有较高的饱和电流,使HTFT具有更好的工作特性,进一步证明了高k材料对于实现高性能晶体管的重要意义.

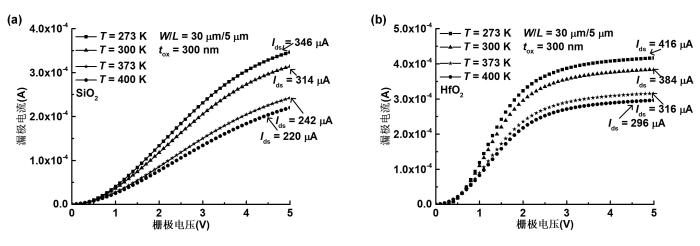

2.4 不同温度条件下TFT的性能对比

图5

图5

不同温度条件下的TFT对应的性能曲线的对比图

Fig. 5

Comparison of the performance curves of TFTs under different temperature conditions

从图中可以看出,晶体管的饱和电流具有负的温度系数,即晶体管的饱和电流随着温度的升高而逐渐减小.从式(5)和式(6)可以看出,栅介质层材料的参数和沟道的宽长比随温度的变化很小,因而影响饱和电流的因素主要是μn和Vth.图6所示为STFT和HTFT的μn和Vth随温度的变化关系.

图6

图6

阈值电压和载流子迁移率随着温度的变化曲线

Fig. 6

Curves of threshhold voltage and carrier mobility as a function of temperature

从图中可以看出,μn和Vth均随着温度的升高而逐渐减小,但是HTFT的μn和Vth均小于STFT的μn和Vth,这是因为随着材料的介电常数的增大,带隙宽度会逐渐减小,因而高k材料制作而成的TFT的开启电压低于传统的SiO2对应的TFT的开启电压.对于载流子迁移率,由于晶体管的有源层使用的材料是Si,因而在Si与SiO2接触的界面态较少,而Si与HfO2接触的界面态则相对较多,这是造成HTFT的载流子迁移率低于STFT的载流子迁移率的重要原因,同时有研究表明,在高k材料中,会存在多种散射机制,其中软声子散射是迁移率退化的主要散射机制[20],另外界面电荷和高k材料中的固定电荷是迁移率退化的重要原因[21].

μn随温度的变化关系可以用式(7)表示:

其中,μn(T)为温度为T时的载流子迁移率,

μn(T0)为温度为300 K时的载流子迁移率,m通常的取值为1.5~2.从器件内部来讲主要是晶格振动散射会随着温度的升高而增强,导致μn的下降.半导体的费米能级随着温度的升高逐渐趋近禁带中央,导致半导体的费米势ФB的下降,因而更容易满足Vs≥2ФB的反型层的形成条件,Vs为硅薄膜上表层的电位,而Vth可以用式(8)表示:

其中,Vox是栅介质层上的电压降.在温度升高时,Vs会随着费米势的下降而下降,最终导致Vth的下降.

综上可以得出,Vth和μn这两者都具有负的温度系数,分别会导致晶体管的饱和电流具有正的温度系数和负的温度系数.而为了获得较高的饱和电流,施加在晶体管栅极上的电压要高于阈值电压,这时晶体管的饱和电流受阈值电压的影响较小,而主要受到载流子迁移率的影响,因而一般情况下,晶体管的饱和电流随温度的升高而减小.这从另一方面也说明晶体管在低温下也可以有很高的工作性能.

通过以上对于不同栅介质尺寸和不同温度条件下的薄膜晶体管的性能研究可以发现,基于高k栅介质材料的HTFT可以实现较小的关态漏电流,较高的电流开关比和较低的亚阈值摆幅,但是由于高k材料与硅薄膜之间存在界面态,因而会导致基于高k栅介质材料的TFT具有较低的载流子迁移率.可以看出界面的质量是影响载流子迁移率的重要因素.对于HfO2而言,其氧扩散率很高因而会影响器件的性能,一种在HfO2中掺杂Al的方法来减小氧扩散的方法被提出,可以有效降低氧扩散率,从而在一定程度上提高器件的工作速度,但是这种方法可能会在一定程度上降低晶体管的开关性能等其他性能.这也就是说对于高k材料可能无法同时获得较高的工作速度和较高的电流开关比.

所以在实际中需要根据具体情况选择合适的高k材料,在需要晶体管的驱动速度较高的情况下可能会牺牲一部分可靠性或者开关性能,在要求晶体管的开关比较高的情况下可能在工作速度方面会有所下降,因而一方面需要不断通过相关的工艺手段尽可能地提高器件的各项工作指标,另一方面在无法同时满足较高的工作速度和较高的可靠性和开关比的情况下,需要根据特定情况下这些指标的重要程度选择合适的材料,比如可以选择介电常数不是很高但是可靠性较高的材料,既获得较高的工作速度,同时获得相对其他高k材料低的但是可接受的电流开关比,即需要在不同性能之间取折中达到最优的工作状态.

3 结 论

通过系统地对基于传统的栅介质材料SiO2和高介电常数的材料HfO2在不同沟道长度和宽度,不同栅介质层厚度和不同温度下的晶体管的建模和性能研究,可以得到晶体管的饱和电流与晶体管的沟道长度和栅介质层的厚度成反比,与沟道宽度成正比,与理论计算结果相一致.可以发现,基于高介电常数材料的薄膜晶体管相对于传统的基于SiO2的薄膜晶体管的优势在于具有较小的关态漏电流,较高的电流开关比和较低的亚阈值摆幅,但是其缺陷在于它的开关速度要低于传统的基于SiO2的薄膜晶体管,因而在实际应用中需要在薄膜晶体管的不同性能指标中进行折中.

参考文献

碳化硅MOSFET电路模型及其应用

Circuit model of silicon carbide MOSFET and its application

非晶硅薄膜晶体管关态电流的物理模型

Physical model of off⁃state current of amorphous silicon thin film transistor

High⁃performance flexible single⁃crystalline silicon nanomembrane thin⁃Film transistors with highk Nb2O5⁃Bi2O3⁃MgO ceramics as gate dielectric on a plastic substrate

High⁃mobility Ge pMOSFETs with crystalline ZrO2 Dielectric

GeSn quantum well P⁃channel tunneling FETs fabricated on Si(001) and (111) with improved subthreshold swing

Half⁃volt operation of IGZO thin⁃film transistors enabled by ultrathin HfO2 gate dielectric

Simulation and analysis of static and dynamic performance of normally⁃off TIVJFET using Sentaurus TCAD

AlGaN/GaN HEMT耐压结构设计与特性研究研究

Research on design and characteristics of pressure⁃resistant structure of AlGaN/GaN HEMT

20 nm high performance enhancement mode InP HEMT with heavily doped S/D regions for future THz applications

Effect of thin gate dielectrics and gate materials on simulated device characteristics of 3D double gate JNT

SOI FinFET器件与组合逻辑电路单粒子效应研究

Research on single event effect of SOI FinFET device and combinational logic circuit

使用Sentaurus TCAD软件设计和研究0

.

Design and study of 0

.

NMOS晶体管的总剂量辐射效应研究

Study on total dose radiation effect of NMOS Transistors

新型MOSFET和TFET器件的辐照可靠性研究

Radiation reliability of new MOSFET and TFET devices

单轴应变Si纳米NMOSFET电特性优化

Optimization of electrical characteristics of uniaxial strained Si nano NMOSFET

一种SOILDMOS器件辐射效应研究研究

Research on radiation effects of SOILDMOS devices

Modeling of radiation damage effects in silicon detectors at high fluences HL⁃LHC with Sentaurus TCAD

堆栈高k栅介质(In)GaAsMOS器件电子迀移率模型及界面特性研究

Electron mobility model and interface characteristics of stacked high⁃k gate dielectric (In)GaAsMOS devices

Simulation study on NMOS gate length variation using TCAD Tool

Effective electron mobility in Si inversion layers in MOS systems with a high⁃k insulator: The role of remote phonon scattering

Remote⁃charge⁃scattering limited mobility in field⁃effect transistors with SiO2 and Al2O3∕SiO2 gate stacks