波束形成技术是在多天线系统中一种利用可变时间延迟和增益来实现旁瓣抑制和选择性的技术,已经广泛应用于无线通信、雷达和射电天文学等领域[1 ] .传统相控阵系统中,通常使用移相器来实现对输入信号的控制,工作频带较窄,但随着信号带宽增加以及整体阵列尺寸增大,使用移相器则会导致波束偏移的现象形成[2 ,3 ] ,从而产生一定的方向误差.而对于真时延单元,其在很宽频带内可以保持恒定的延时[4 ,5 ] ,避免了信号因偏离工作频率而导致的波束偏移.因此真时延阵列处理是必要的.

在宽带系统下,形成多波束对于容量和数据速度的增加至关重要[6 ] .然而,由于信号流图(Signal Flow Graghs,SFG)的潜在复杂性,多波束收发机的实现十分困难.传统的多波束形成网络,如巴特勒矩阵[7 ] ,采用移相器单元,适合频带较窄的通信系统.Blass矩阵、Nolen矩阵[8 ,9 ] 都属于真时延系统,它们使用了计算机编码算法来设计网络,虽适用于宽带通信系统,但在低频通信时由于大的延迟时间会占用大量芯片面积.龚建强等[10 ] 利用新型SCRLH传输线实现了超宽带的滤波器,可实现无衰减相移,但微带实现所占面积太大.

近年来有源全通滤波器(All Pass Filter,APF)逐渐引起人们的关注.一方面在低GHz级别的工作频带下,相比于传输线以及LC网络[11 ,12 ] 等传统真时延单元对硅片的大面积占用,并随着天线阵规模的增大无法满足延时范围的要求,有源滤波器利用晶体管跨导特性代替了传统的LC网络,杜绝了大面积电感,从而获得了较小的尺寸;另一方面,有源滤波器的可调性好,可以进行高精度延时、增益控制,并且可通过级联等方式增加最大延时,如Gm⁃RC全通滤波器、Gm⁃C全通滤波器[13 ,14 ] .

为了充分利用有源真时延单元的小面积、低延时波动等优点,本文提出一种基于有源真时延技术的低复杂度波束形成架构,相比于传统的链路式架构,在输出四个波束时总延时单元数量降低了14个,进一步降低了芯片面积.设计并实现四入四出波束形成器,工作频段为0.3 G~1 GHz,采用改进的一阶全通滤波器代替传统无源延时单元,在环状网络延时架构的基础上进行改进,以信号单向流动的方式去除信号的冲突,并实现了模块复用,获得了稳定的群延时.

1 系统架构

图1 所示为传统多波束天线阵列接收器.若输出单个波束,信号从某一角度平行入射,到达地面上间距为d 的一组天线阵列,入射角θ ,相邻两天线接收到信号的时间差τ = d s i n θ c c 是波速.想要同时获得N 个波束输出则需要N 个延时网络,这使得延时单元数量成倍增加,严重限制可形成的波束数量以及天线规模.如四入四出时,传统穷举多波束结构总延时数为48τ ,而Blass多波束结构总延时数为45τ [8 ] .

图1

图1

真时延多波束天线阵列接收器

Fig.1

TTD multiple antennas array receiver

图2 所示为本文的新型基于有源真时延技术的多波束形成架构图,该多波束形成架构可同时接收四路差分信号以及输出四路差分信号.该架构包括四条传输延时线,信号经过低噪声放大器的放大后,通过控制延时路径长短产生精确延时,对每个天线的RF信号进行一定延时,弥补信号到达天线的延时差,并定向传输到不同的加法器进行合成.考虑到延时单元的群延时会受输出端负载值的影响,设计避免了不同信号从同一真时延单元输出,并在所有未接入加法器的真时延单元输出端添加一个标准负载,以保证延时的稳定性和一致性.

图2

图2

本文提出的基于有源真时延的波束形成架构

Fig.2

Proposed beamformer architecture based on active true⁃time delay

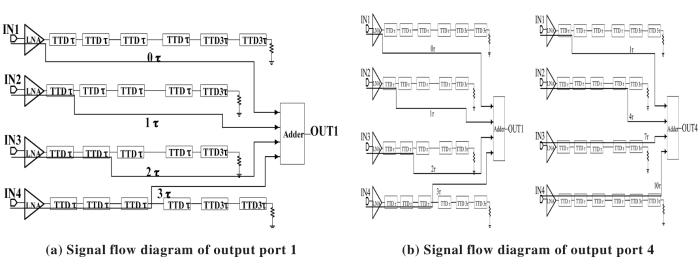

图3 a和图3 b展示了来自空间中的RF信号入射到天线阵列后的流动情况.信号从天线1,2,3,4到输出端口1的延时分别为0τ, 1τ, 2τ, 3τ ,相邻天线间的延时差是τ ;信号从天线1,2,3,4到输出端口4的延时分别为1τ, 4τ, 7τ, 10τ, 相邻天线间的延时差是3τ .由于延时间隔相同,因此来自某一固定方向的RF信号可以通过线性天线阵列在输出端口进行同相相干叠加,实现角度为θ 的波束角度.同理OUT2和OUT3也相应实现对称角度的波束,因此实现了四个方向的波束.

图3

图3

波束形成架构信号流向图

Fig.3

Signal flow diagram of the beamformer architecture

本文所提出的架构的优点在于通过有源延时单元的路径共享,不仅降低了延时单元数量,节省了大量面积,而且获得比无源单元更加稳定的群延时,网络化的结构也使得系统可以同时得到多个波束输出.

2 电路结构

2.1 低噪声放大器

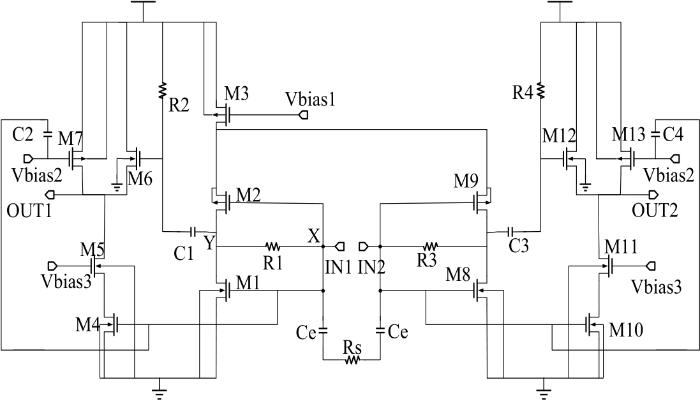

采用噪声抵消技术[15 ] 的宽带低噪声放大器,不仅能放大从天线接收的微弱信号,还有改善噪声特性、提高信噪比的作用.本文所设计的差分低噪声放大器如图4 所示.

图4

图4

差分低噪声放大器结构原理图

Fig.4

Schematic diagram of the differential LNA

差分低噪声放大器电路左右对称,现就单独一半进行分析:其输入阻抗可表示为:

Z i n = 1 g m 1 + g m 2 1 + R 1 R L (1)

其中gm 1 和gm 2 是M1和M2的跨导,R L 表示M1和M2的并联输出阻抗,其值远大于R 1 .当Z in =R s /2,M1的沟道热噪声是在亚微米CMOS器件中的主要噪声,可以建模为一个噪声电流源In .一部分热噪声电流αIn (0<α <1)通过R 1 和R s /2流出M1,并导致两个处于阵列中的相关的噪声电压节点X和Y能被表示为:

V X , n = α I n R s / 2 (2)

V Y , n = α I n ( R 1 + R s / 2 ) (3)

V Y , n V X , n = R 1 + R s / 2 R s / 2 (4)

V X,n 经过M4放大到输出,在传统的噪声消除结构,第二级电压增益是:

A v 2 = g m 4 1 g m 6 / / R L 2 (5)

其中,gm 4 和gm 6 分别是M4和M6的跨导,R L2 约为M7的输出阻抗,这是由于共源共栅结构M4和M5的输出阻抗远大于R ds7 .当负载为50 Ω,第二级的电压增益为Av 2 /2,M6的电压增益为0.5,则其输出噪声电压可以表示为:

V o u t , n = V Y , n / 2 - V X , n A v 2 / 2 (6)

A v 2 = R f + R s / 2 R s / 2 (7)

本文提出的LNA中,输入节点处的信号通过电容耦合到附加偏置晶体管M7.所以当负载为50 Ω时,其电压增益为:

A v 2 ' = g m 4 + g m 7 2 g m 6 (8)

式(8)表明,在M7的帮助下,可用更小的M4器件来满足噪声消除条件,因而减小了电流和芯片面积.此外,由M1,M2构成的反相器结构,通过使用电流多路复用来降低功耗,调整其尺寸,可实现差分输入阻抗匹配.共源共栅晶体管M4提高了绝缘性和通过减少来自M5的密勒效应来降低了输入电容.

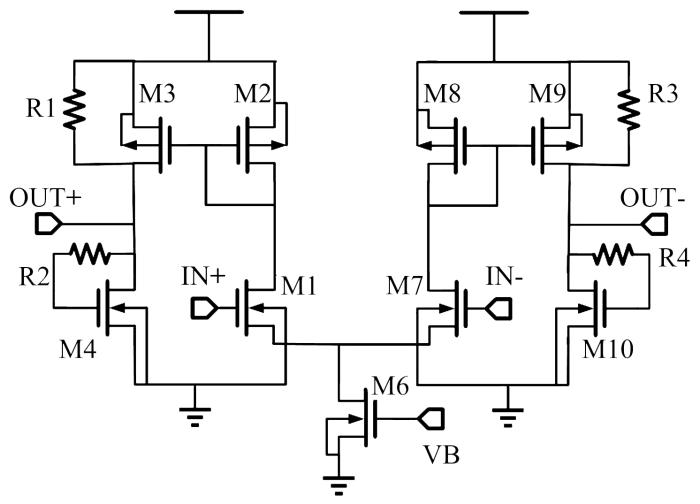

2.2 真时延架构

延时系统是波束形成芯片最重要的模块,延时单元的输入输出阻抗、延时精度、频带内的延时起伏等指标决定了波束形成的效果.传输线、LC网络等无源延时单元虽然能获得较大的延时,但随着级联数的增加,电感、电容所使用的数量则越来越多,导致占用芯片面积较大,且信号可双向流动,在网络架构中易造成信号的冲突.本文采用有源真时延技术,设计的有源滤波器结构如图5 所示,其芯片面积大幅度减小.

图5

图5

Gm⁃C有源滤波器原理图

Fig.5

Schematic diagram of the Gm⁃C active filter

晶体管M1,M2,M3,M4实现了一个增益为1的低通信号路径,电阻R1与M4的组合为后级的晶体管提供与输入相同的偏置电压,即V out,DC =V in,DC .另外,NMOS和PMOS管的电流实现了复用,降低了功耗.与传统的Gm⁃RC全通滤波器[14 ] 相比,去除了可变电容的使用,使得面积进一步降低.该延时电路的传输函数和低频下的延时时间为:

A v ( s ) = V o u t V i n ( s ) = g m 1 g m 3 R L g m 2 + s C g s (9)

τ ≈ C g s g m 2 (10)

其中,C gs 为M2和M3晶体管的寄生电容C gs2 /C gs3 的值,RL 是输出端的负载阻值.

通过分析,M4也会在输出端引入寄生电容C gs4 ,由此产生一个不希望的极点和获得额外的延时,同时降低了有效带宽.因此本设计采用有源电感峰化技术,通过添加电阻R2到M4的栅极和漏极之间,将M4转换为一个“有源电感”.该有源电感器的阻抗为:

Z A - i n d ( s ) = 1 g m 4 s R 2 C g s 4 + 1 s C g s 4 g m 4 + 1 (11)

选择合适的R 2 =1/gm 4 ,使得Z A⁃ind =1/gm 4 ,可有效扩展带宽.图6 展示了添加电阻R2前后的真时延单元增益仿真对比,可看出电阻R2对带宽的提高有显著效果.综合考虑偏置、匹配等各种因素,优化各晶体管和电阻参数,就能得到所需群延时.

图6

图6

电阻R2对真时延单元增益的影响

Fig.6

Influence of R2 on gain of the true⁃time delay unit

2.3 加法器

加法器完成的功能是检测各路延时链合适的节点信号,汇聚成一路信号,最终叠加输出.电路设计中,在电流域中实现加法比在电压域中更容易实现,如采用电流镜实现,晶体管本身扮演者电压控制电流源器件,栅极检测电压,转换成漏极电流,通过镜像管叠加电流输出.考虑到本设计的工艺为BiCMOS工艺,HBT异质结三极管在提供更优越的高频特性的同时,非线性程度也更低.因此本文采用HBT三极管设计了加法器,利用零点成峰放大器技术优化带宽,其原理图如图7 所示.

图7

图7

加法器原理图

Fig.7

Schematic diagram of the adder

加法器由两级构成,第一级是跟随器,检测电压提供缓冲,缓解第二级的输入电阻对延时链节点的影响.第二级是零点成峰放大器,通过在三极管Q2 的发射级电阻上并联一个电容C1 给电路传输函数增加一个零点来改善带宽.最终,检测到的电压信号转换成电流信号汇聚到公共节点COM处,并在公共电阻RCOM 处产生所需的叠加了的电压信号输出给最后的输出匹配级.X处产生的极点由寄生电容和三极管Q1 的跨导决定,在合适的偏置下Q1 跨导足够大以至于该极点远远大于本电路工作带宽,因此可以忽略它的影响.由于第一级的增益约等于1,所以整个加法器的增益由第二级决定:

A v ( s ) = V C O M V X = R C O M 1 g Q 2 ( 1 + s R 1 C 1 ) + R 1 × 1 + s R 1 C 1 1 + s R C O M C L ≈ R C O M R 1 1 + s R 1 C 1 1 + s R C O M C L (12)

可见,当第二级的跨导g Q2 足够大时,增益取决于负载电阻RCOM 与发射机串联电阻R1 的比值.带宽可以通过电容C1 调节使得零点小于等于极点从而达到扩展带宽的目的.

3 版图设计与仿真结果

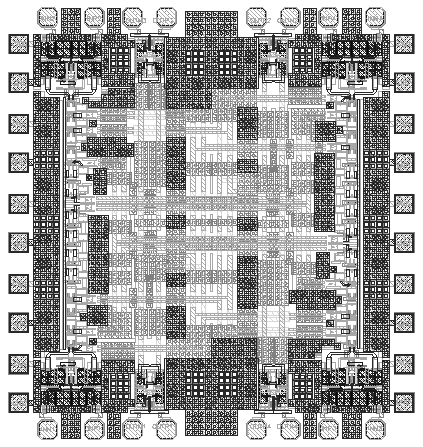

本文设计的多波束形成芯片由多级电路组成,相对带宽超过100%,并在设计过程中重点考虑了器件的摆放和信号线的走向.采用HHNEC 0.18 μm BiCMOS工艺,图8 为波束形成电路的版图,在所有端口添加了ESD保护电路,包含PAD的芯片总面积为2.0 mm×1.9 mm.使用Cadence Spectre RF仿真器进行后仿真.在供电电压为1.8 V时,功耗为396 mW.工作频率0.3 G~1 GHz,图9 为不同输出端的合成增益仿真结果,不同路增益随着延时级数的增加而略微增大,但在整个宽带内基本保持恒定,总增益约为25 dB,起伏不超过3 dB.

图8

图8

波束形成器版图

Fig. 8

Layout of the beamformer

图9

图9

波束形成器总增益仿真结果

Fig.9

Simulation results of total gain of the beamformer

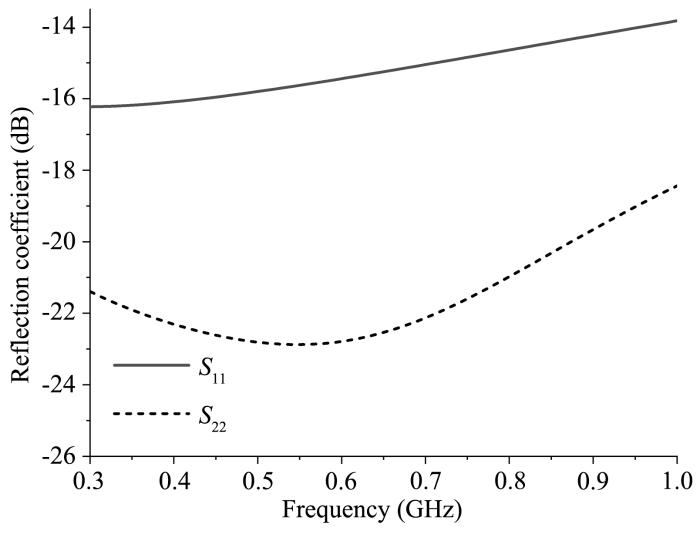

图10 为输入端口的反射系数S 11 和输出端口的反射系数S 22 ,整个频带内S 11 低于-13.8 dB,S 22 低于-18 dB.在输出1和4上,每个波束的群延时仿真如图11 ,相邻波束的时延差分别为103 ps和309 ps.由于结构的中心对称性,到输出2的群延时与到输出1的群延关系为:IO11=IO42,IO21=IO32,IO31=IO22,IO41=IO12.到输出3的群延时与到输出4的群延时关系同理.图12 展示了根据仿真数据在matlab所生成的波束形成器方向图,各波束增益基本保持一致,误差在1.5 dB以内,并随着频率的上升,天线阵的方向性越来越好.

图10

图10

波束形成器S 11 与S 22 仿真结果

Fig.10

Simulation results of S 11 and S 22 of the beamformer

图11

图11

波束形成器群延时仿真结果

Fig. 11

Simulation results of group delay of the beamformer

图12

图12

波束形成器方向性仿真结果(650 MHz和1000 MHz)

Fig.12

Simulation results of direction of the beamformer(650 MHz and 1000 MHz)

表1 总结了本文设计的电路和其他近几年提出的波束形成电路主要性能对比.采用有源全通滤波器实现延时,通过路径共享,实现了低复杂度,与LC网络方式相比面积优势明显,与具同样功能的文献[11 ]比较,面积节省了80%.与同种延时方式相比,本设计能实现多个波束同时输出,且有着较低的延时波动.综上所述,本文提出的波束形成器有着小面积、多波束、延时精度高等优点,综合性能良好.

4 结 论

本文提出了一种基于有源真时延技术的低复杂度波束形成架构,通过对真时延单元共享,比传统的多波束形成架构节省了30%的真时延单元.在此基础上,基于HHNEC 0.18 μm BiCMOS工艺设计了一种全集成四入四出波束形成器,工作频段为0.3 G~1 GHz.所设计波束形成器的单通道最大延时波动为2.4%,具

有极高的延时稳定性.结合有源真延时单元的小尺寸特点,最终面积为3.8 mm2 ,比同功能无源波束形成结构节省80%的面积,降低成本,适用于超宽带雷达、通信和射电天文等领域.

参考文献

View Option

[1]

Ahmadi P , Taghavi M H , Belostotski L ,et al . 6⁃GHz all⁃pass⁃filter⁃based delay⁃and⁃sum beam⁃former in 130 nm CMOS∥2014 IEEE 57th International Midwest Symposium on Circuits and Systems (MWSCAS)

College Station,TX,USA :IEEE ,2014 :837 -840 .

[本文引用: 5]

[2]

Ariyarathna V , Udayanga N , Madanayake A ,et al . Design methodology of an analog 9⁃beam squint⁃free wideband IF multi⁃beamformer for mmW applications∥2017 Moratuwa Engineering Research Conference

Moratuwa,Sri Lanka :IEEE ,2017 : 236 .

[本文引用: 1]

[3]

Moallemi S , Welker R , Kitchen J . Wide band programmable true time delay block for phased array antenna applications∥2016 IEEE Dallas Circuits and Systems Conference

Arlington,TX,USA :IEEE ,2016 :1 -4 .

[本文引用: 1]

[4]

Chu T S , Hashemi H . A true time⁃delay⁃based bandpass multi⁃beam array at mm⁃waves supporting instantaneously wide bandwidths∥ 2010 IEEE International Solid⁃State Circuits Conference

San Francisco,CA,USA :IEEE ,2010 :38 -39 .

[本文引用: 6]

[5]

Park S , Jeon S . A 15~40 GHz CMOS True⁃time delay circuit for UWB multi⁃antenna systems

IEEE Microwave and Wireless Components Letters ,2013 ,23 (3 ):149 -151 .

[本文引用: 1]

[6]

Rangan S , Rappaport T S , Erkip E . Millimeter⁃wave cellular wireless networks: potentials and challenges

Proceedings of the IEEE ,2014 ,102 (3 ):366 -385 .

[本文引用: 1]

[7]

Kang D W , Koh K J , Rebeiz G M . A Ku ⁃band two⁃antenna four⁃simultaneous beams SiGe BiCMOS phased array receiver

IEEE Transactions on Microwave Theory and Techniques ,2010 ,58 (4 ):771 -780 .

[本文引用: 1]

[8]

Chu T S , Hashemi H . True⁃time⁃delay⁃based multi⁃beam arrays

IEEE Transactions on Microwave Theory and Techniques ,2013 ,61 (8 ):3072 -3082 .

[本文引用: 2]

[9]

Djerafi T , Fonseca N J G , Wu K . Broadband substrate integrated waveguide 4×4 nolen matrix based on coupler delay compensation

IEEE Transactions on Microwave Theory and Techniques ,2011 ,59 (7 ):1740 -1745 .

[本文引用: 1]

[10]

龚建强 ,褚庆昕 . 一种新型SCRLH传输线结构的设计与分析

华南理工大学学报(自然科学版) ,2009 ,37 (9 ):52 -56 .

[本文引用: 1]

Gong J Q , Chu Q X . Design and analysis of a novel SCRLH transmission line structure

Journal of South China University of Technology (Natural Science Edition) ,2009 ,37 (9 ):52 -56 .

[本文引用: 1]

[11]

Liu Y Z , Zhang W , Liu Y Y . A fully integrated 4⁃channel beamformer based on TTD phased array in 0

.18 μm CMOS. Microelectronics Journal ,2018 ,80 :81 -86 .

[本文引用: 3]

[12]

Chu T S , Roderick J , Hashemi H . An integrated ultra⁃wideband timed array receiver in 013 μm CMOS using a path⁃sharing true time delay architecture.

.IEEE Journal of Solid⁃State Circuits ,2007 ,42 (12 ):2834 -2850 .

[本文引用: 2]

[13]

Garakoui S K , Klumperink E A M , Nauta B ,et al . Compact cascadable gm⁃C all⁃pass true time delay cell with reduced delay variation over frequency

IEEE Journal of Solid⁃State Circuits ,2015 ,50 (3 ):693 -703 .

[本文引用: 2]

[14]

Garakoui S K , Klumperink E A M , Nauta B ,et al . A 1⁃to⁃2.5GHz phased⁃array IC based on gm⁃RC all⁃pass time⁃delay cells∥2012 IEEE International Solid⁃State Circuits Conference.

San Francisco,CA,USA :IEEE ,2012 :80 -82 .

[本文引用: 2]

[15]

Li M , Wang Z G , Xu J ,et al . A 500 kHz~1.4GHz push⁃pull differential noise cancellation LNA∥2015 IEEE International Conference on Communication Software and Networks.

Chengdu,China :IEEE ,2015 :182 -185 .

[本文引用: 1]

[16]

Ahmadi P , Belostotski L , Madanayake A ,et al . 0 .96 ⁃to⁃ 5 .1 GHz 4⁃element spatially analog IIR⁃enhanced delay⁃and⁃sum beamformer∥2017 IEEE MTT⁃S International Microwave Symposium

Honololu,HI,USA :IEEE ,2017 :1610 -1613 .

[本文引用: 1]

6?GHz all?pass?filter?based delay?and?sum beam?former in 130 nm CMOS∥2014 IEEE 57th International Midwest Symposium on Circuits and Systems (MWSCAS)

5

2014

... 波束形成技术是在多天线系统中一种利用可变时间延迟和增益来实现旁瓣抑制和选择性的技术,已经广泛应用于无线通信、雷达和射电天文学等领域[1 ] .传统相控阵系统中,通常使用移相器来实现对输入信号的控制,工作频带较窄,但随着信号带宽增加以及整体阵列尺寸增大,使用移相器则会导致波束偏移的现象形成[2 ,3 ] ,从而产生一定的方向误差.而对于真时延单元,其在很宽频带内可以保持恒定的延时[4 ,5 ] ,避免了信号因偏离工作频率而导致的波束偏移.因此真时延阵列处理是必要的. ...

... Performance comparison between this paper and other literatures

Table 1 参数 文献[11 ] 文献[12 ] 文献[13 ] 文献[16 ] 本文 工艺 0.18 μm 0.13 μm 0.14 μm 0.13 μm 0.18 μm 带宽(GHz) 0.35~1 1~15 1~2.5 0.96~5.1 0.3~1 延时通道 4 4 4 4 4 输出端口个数 4 1 1 1 4 延时范围(ps) 0~720 0~225 0~550 0~82 0~1030 延时波动 N.A. *14% 2% N.A. 2.4% 增益(dB) 18.5 24 ~12 ~21 25 功耗(mW) 234 555 450 **30.6~52.5 396 面积(mm2 ) 19.995 9.92 1 N.A. 3.8 真时延技术 LC LC Gm⁃C Gm⁃C Gm⁃C

注: *根据所给延时响应估算的值,~每通道增益,**每通道功耗 ...

...

1 1 4 延时范围(ps) 0~720 0~225 0~550 0~82 0~1030 延时波动 N.A. *14% 2% N.A. 2.4% 增益(dB) 18.5 24 ~12 ~21 25 功耗(mW) 234 555 450 **30.6~52.5 396 面积(mm2 ) 19.995 9.92 1 N.A. 3.8 真时延技术 LC LC Gm⁃C Gm⁃C Gm⁃C 注: *根据所给延时响应估算的值,~每通道增益,**每通道功耗 ...

...

1 4 延时范围(ps) 0~720 0~225 0~550 0~82 0~1030 延时波动 N.A. *14% 2% N.A. 2.4% 增益(dB) 18.5 24 ~12 ~21 25 功耗(mW) 234 555 450 **30.6~52.5 396 面积(mm2 ) 19.995 9.92 1 N.A. 3.8 真时延技术 LC LC Gm⁃C Gm⁃C Gm⁃C 注: *根据所给延时响应估算的值,~每通道增益,**每通道功耗 ...

...

1 N.A. 3.8 真时延技术 LC LC Gm⁃C Gm⁃C Gm⁃C 注: *根据所给延时响应估算的值,~每通道增益,**每通道功耗 ...

Design methodology of an analog 9?beam squint?free wideband IF multi?beamformer for mmW applications∥2017 Moratuwa Engineering Research Conference

1

2017

... 波束形成技术是在多天线系统中一种利用可变时间延迟和增益来实现旁瓣抑制和选择性的技术,已经广泛应用于无线通信、雷达和射电天文学等领域[1 ] .传统相控阵系统中,通常使用移相器来实现对输入信号的控制,工作频带较窄,但随着信号带宽增加以及整体阵列尺寸增大,使用移相器则会导致波束偏移的现象形成[2 ,3 ] ,从而产生一定的方向误差.而对于真时延单元,其在很宽频带内可以保持恒定的延时[4 ,5 ] ,避免了信号因偏离工作频率而导致的波束偏移.因此真时延阵列处理是必要的. ...

Wide band programmable true time delay block for phased array antenna applications∥2016 IEEE Dallas Circuits and Systems Conference

1

2016

... 波束形成技术是在多天线系统中一种利用可变时间延迟和增益来实现旁瓣抑制和选择性的技术,已经广泛应用于无线通信、雷达和射电天文学等领域[1 ] .传统相控阵系统中,通常使用移相器来实现对输入信号的控制,工作频带较窄,但随着信号带宽增加以及整体阵列尺寸增大,使用移相器则会导致波束偏移的现象形成[2 ,3 ] ,从而产生一定的方向误差.而对于真时延单元,其在很宽频带内可以保持恒定的延时[4 ,5 ] ,避免了信号因偏离工作频率而导致的波束偏移.因此真时延阵列处理是必要的. ...

A true time?delay?based bandpass multi?beam array at mm?waves supporting instantaneously wide bandwidths∥ 2010 IEEE International Solid?State Circuits Conference

6

2010

... 波束形成技术是在多天线系统中一种利用可变时间延迟和增益来实现旁瓣抑制和选择性的技术,已经广泛应用于无线通信、雷达和射电天文学等领域[1 ] .传统相控阵系统中,通常使用移相器来实现对输入信号的控制,工作频带较窄,但随着信号带宽增加以及整体阵列尺寸增大,使用移相器则会导致波束偏移的现象形成[2 ,3 ] ,从而产生一定的方向误差.而对于真时延单元,其在很宽频带内可以保持恒定的延时[4 ,5 ] ,避免了信号因偏离工作频率而导致的波束偏移.因此真时延阵列处理是必要的. ...

... Performance comparison between this paper and other literatures

Table 1 参数 文献[11 ] 文献[12 ] 文献[13 ] 文献[16 ] 本文 工艺 0.18 μm 0.13 μm 0.14 μm 0.13 μm 0.18 μm 带宽(GHz) 0.35~1 1~15 1~2.5 0.96~5.1 0.3~1 延时通道 4 4 4 4 4 输出端口个数 4 1 1 1 4 延时范围(ps) 0~720 0~225 0~550 0~82 0~1030 延时波动 N.A. *14% 2% N.A. 2.4% 增益(dB) 18.5 24 ~12 ~21 25 功耗(mW) 234 555 450 **30.6~52.5 396 面积(mm2 ) 19.995 9.92 1 N.A. 3.8 真时延技术 LC LC Gm⁃C Gm⁃C Gm⁃C

注: *根据所给延时响应估算的值,~每通道增益,**每通道功耗 ...

...

4 4 4 4 输出端口个数 4 1 1 1 4 延时范围(ps) 0~720 0~225 0~550 0~82 0~1030 延时波动 N.A. *14% 2% N.A. 2.4% 增益(dB) 18.5 24 ~12 ~21 25 功耗(mW) 234 555 450 **30.6~52.5 396 面积(mm2 ) 19.995 9.92 1 N.A. 3.8 真时延技术 LC LC Gm⁃C Gm⁃C Gm⁃C 注: *根据所给延时响应估算的值,~每通道增益,**每通道功耗 ...

...

4 4 4 输出端口个数 4 1 1 1 4 延时范围(ps) 0~720 0~225 0~550 0~82 0~1030 延时波动 N.A. *14% 2% N.A. 2.4% 增益(dB) 18.5 24 ~12 ~21 25 功耗(mW) 234 555 450 **30.6~52.5 396 面积(mm2 ) 19.995 9.92 1 N.A. 3.8 真时延技术 LC LC Gm⁃C Gm⁃C Gm⁃C 注: *根据所给延时响应估算的值,~每通道增益,**每通道功耗 ...

...

4 4 输出端口个数 4 1 1 1 4 延时范围(ps) 0~720 0~225 0~550 0~82 0~1030 延时波动 N.A. *14% 2% N.A. 2.4% 增益(dB) 18.5 24 ~12 ~21 25 功耗(mW) 234 555 450 **30.6~52.5 396 面积(mm2 ) 19.995 9.92 1 N.A. 3.8 真时延技术 LC LC Gm⁃C Gm⁃C Gm⁃C 注: *根据所给延时响应估算的值,~每通道增益,**每通道功耗 ...

...

4 1 1 1 4 延时范围(ps) 0~720 0~225 0~550 0~82 0~1030 延时波动 N.A. *14% 2% N.A. 2.4% 增益(dB) 18.5 24 ~12 ~21 25 功耗(mW) 234 555 450 **30.6~52.5 396 面积(mm2 ) 19.995 9.92 1 N.A. 3.8 真时延技术 LC LC Gm⁃C Gm⁃C Gm⁃C 注: *根据所给延时响应估算的值,~每通道增益,**每通道功耗 ...

A 15~40 GHz CMOS True?time delay circuit for UWB multi?antenna systems

1

2013

... 波束形成技术是在多天线系统中一种利用可变时间延迟和增益来实现旁瓣抑制和选择性的技术,已经广泛应用于无线通信、雷达和射电天文学等领域[1 ] .传统相控阵系统中,通常使用移相器来实现对输入信号的控制,工作频带较窄,但随着信号带宽增加以及整体阵列尺寸增大,使用移相器则会导致波束偏移的现象形成[2 ,3 ] ,从而产生一定的方向误差.而对于真时延单元,其在很宽频带内可以保持恒定的延时[4 ,5 ] ,避免了信号因偏离工作频率而导致的波束偏移.因此真时延阵列处理是必要的. ...

Millimeter?wave cellular wireless networks: potentials and challenges

1

2014

... 在宽带系统下,形成多波束对于容量和数据速度的增加至关重要[6 ] .然而,由于信号流图(Signal Flow Graghs,SFG)的潜在复杂性,多波束收发机的实现十分困难.传统的多波束形成网络,如巴特勒矩阵[7 ] ,采用移相器单元,适合频带较窄的通信系统.Blass矩阵、Nolen矩阵[8 ,9 ] 都属于真时延系统,它们使用了计算机编码算法来设计网络,虽适用于宽带通信系统,但在低频通信时由于大的延迟时间会占用大量芯片面积.龚建强等[10 ] 利用新型SCRLH传输线实现了超宽带的滤波器,可实现无衰减相移,但微带实现所占面积太大. ...

A Ku ?band two?antenna four?simultaneous beams SiGe BiCMOS phased array receiver

1

2010

... 在宽带系统下,形成多波束对于容量和数据速度的增加至关重要[6 ] .然而,由于信号流图(Signal Flow Graghs,SFG)的潜在复杂性,多波束收发机的实现十分困难.传统的多波束形成网络,如巴特勒矩阵[7 ] ,采用移相器单元,适合频带较窄的通信系统.Blass矩阵、Nolen矩阵[8 ,9 ] 都属于真时延系统,它们使用了计算机编码算法来设计网络,虽适用于宽带通信系统,但在低频通信时由于大的延迟时间会占用大量芯片面积.龚建强等[10 ] 利用新型SCRLH传输线实现了超宽带的滤波器,可实现无衰减相移,但微带实现所占面积太大. ...

True?time?delay?based multi?beam arrays

2

2013

... 在宽带系统下,形成多波束对于容量和数据速度的增加至关重要[6 ] .然而,由于信号流图(Signal Flow Graghs,SFG)的潜在复杂性,多波束收发机的实现十分困难.传统的多波束形成网络,如巴特勒矩阵[7 ] ,采用移相器单元,适合频带较窄的通信系统.Blass矩阵、Nolen矩阵[8 ,9 ] 都属于真时延系统,它们使用了计算机编码算法来设计网络,虽适用于宽带通信系统,但在低频通信时由于大的延迟时间会占用大量芯片面积.龚建强等[10 ] 利用新型SCRLH传输线实现了超宽带的滤波器,可实现无衰减相移,但微带实现所占面积太大. ...

... 图1 所示为传统多波束天线阵列接收器.若输出单个波束,信号从某一角度平行入射,到达地面上间距为d 的一组天线阵列,入射角θ ,相邻两天线接收到信号的时间差τ = d s i n θ c c 是波速.想要同时获得N 个波束输出则需要N 个延时网络,这使得延时单元数量成倍增加,严重限制可形成的波束数量以及天线规模.如四入四出时,传统穷举多波束结构总延时数为48τ ,而Blass多波束结构总延时数为45τ [8 ] . ...

Broadband substrate integrated waveguide 4×4 nolen matrix based on coupler delay compensation

1

2011

... 在宽带系统下,形成多波束对于容量和数据速度的增加至关重要[6 ] .然而,由于信号流图(Signal Flow Graghs,SFG)的潜在复杂性,多波束收发机的实现十分困难.传统的多波束形成网络,如巴特勒矩阵[7 ] ,采用移相器单元,适合频带较窄的通信系统.Blass矩阵、Nolen矩阵[8 ,9 ] 都属于真时延系统,它们使用了计算机编码算法来设计网络,虽适用于宽带通信系统,但在低频通信时由于大的延迟时间会占用大量芯片面积.龚建强等[10 ] 利用新型SCRLH传输线实现了超宽带的滤波器,可实现无衰减相移,但微带实现所占面积太大. ...

一种新型SCRLH传输线结构的设计与分析

1

2009

... 在宽带系统下,形成多波束对于容量和数据速度的增加至关重要[6 ] .然而,由于信号流图(Signal Flow Graghs,SFG)的潜在复杂性,多波束收发机的实现十分困难.传统的多波束形成网络,如巴特勒矩阵[7 ] ,采用移相器单元,适合频带较窄的通信系统.Blass矩阵、Nolen矩阵[8 ,9 ] 都属于真时延系统,它们使用了计算机编码算法来设计网络,虽适用于宽带通信系统,但在低频通信时由于大的延迟时间会占用大量芯片面积.龚建强等[10 ] 利用新型SCRLH传输线实现了超宽带的滤波器,可实现无衰减相移,但微带实现所占面积太大. ...

一种新型SCRLH传输线结构的设计与分析

1

2009

... 在宽带系统下,形成多波束对于容量和数据速度的增加至关重要[6 ] .然而,由于信号流图(Signal Flow Graghs,SFG)的潜在复杂性,多波束收发机的实现十分困难.传统的多波束形成网络,如巴特勒矩阵[7 ] ,采用移相器单元,适合频带较窄的通信系统.Blass矩阵、Nolen矩阵[8 ,9 ] 都属于真时延系统,它们使用了计算机编码算法来设计网络,虽适用于宽带通信系统,但在低频通信时由于大的延迟时间会占用大量芯片面积.龚建强等[10 ] 利用新型SCRLH传输线实现了超宽带的滤波器,可实现无衰减相移,但微带实现所占面积太大. ...

A fully integrated 4?channel beamformer based on TTD phased array in 0

3

2018

... 近年来有源全通滤波器(All Pass Filter,APF)逐渐引起人们的关注.一方面在低GHz级别的工作频带下,相比于传输线以及LC网络[11 ,12 ] 等传统真时延单元对硅片的大面积占用,并随着天线阵规模的增大无法满足延时范围的要求,有源滤波器利用晶体管跨导特性代替了传统的LC网络,杜绝了大面积电感,从而获得了较小的尺寸;另一方面,有源滤波器的可调性好,可以进行高精度延时、增益控制,并且可通过级联等方式增加最大延时,如Gm⁃RC全通滤波器、Gm⁃C全通滤波器[13 ,14 ] . ...

... 表1 总结了本文设计的电路和其他近几年提出的波束形成电路主要性能对比.采用有源全通滤波器实现延时,通过路径共享,实现了低复杂度,与LC网络方式相比面积优势明显,与具同样功能的文献[11 ]比较,面积节省了80%.与同种延时方式相比,本设计能实现多个波束同时输出,且有着较低的延时波动.综上所述,本文提出的波束形成器有着小面积、多波束、延时精度高等优点,综合性能良好. ...

... Performance comparison between this paper and other literatures

Table 1 参数 文献[11 ] 文献[12 ] 文献[13 ] 文献[16 ] 本文 工艺 0.18 μm 0.13 μm 0.14 μm 0.13 μm 0.18 μm 带宽(GHz) 0.35~1 1~15 1~2.5 0.96~5.1 0.3~1 延时通道 4 4 4 4 4 输出端口个数 4 1 1 1 4 延时范围(ps) 0~720 0~225 0~550 0~82 0~1030 延时波动 N.A. *14% 2% N.A. 2.4% 增益(dB) 18.5 24 ~12 ~21 25 功耗(mW) 234 555 450 **30.6~52.5 396 面积(mm2 ) 19.995 9.92 1 N.A. 3.8 真时延技术 LC LC Gm⁃C Gm⁃C Gm⁃C

注: *根据所给延时响应估算的值,~每通道增益,**每通道功耗 ...

An integrated ultra?wideband timed array receiver in 013 μm CMOS using a path?sharing true time delay architecture.

2

2007

... 近年来有源全通滤波器(All Pass Filter,APF)逐渐引起人们的关注.一方面在低GHz级别的工作频带下,相比于传输线以及LC网络[11 ,12 ] 等传统真时延单元对硅片的大面积占用,并随着天线阵规模的增大无法满足延时范围的要求,有源滤波器利用晶体管跨导特性代替了传统的LC网络,杜绝了大面积电感,从而获得了较小的尺寸;另一方面,有源滤波器的可调性好,可以进行高精度延时、增益控制,并且可通过级联等方式增加最大延时,如Gm⁃RC全通滤波器、Gm⁃C全通滤波器[13 ,14 ] . ...

... Performance comparison between this paper and other literatures

Table 1 参数 文献[11 ] 文献[12 ] 文献[13 ] 文献[16 ] 本文 工艺 0.18 μm 0.13 μm 0.14 μm 0.13 μm 0.18 μm 带宽(GHz) 0.35~1 1~15 1~2.5 0.96~5.1 0.3~1 延时通道 4 4 4 4 4 输出端口个数 4 1 1 1 4 延时范围(ps) 0~720 0~225 0~550 0~82 0~1030 延时波动 N.A. *14% 2% N.A. 2.4% 增益(dB) 18.5 24 ~12 ~21 25 功耗(mW) 234 555 450 **30.6~52.5 396 面积(mm2 ) 19.995 9.92 1 N.A. 3.8 真时延技术 LC LC Gm⁃C Gm⁃C Gm⁃C

注: *根据所给延时响应估算的值,~每通道增益,**每通道功耗 ...

Compact cascadable gm?C all?pass true time delay cell with reduced delay variation over frequency

2

2015

... 近年来有源全通滤波器(All Pass Filter,APF)逐渐引起人们的关注.一方面在低GHz级别的工作频带下,相比于传输线以及LC网络[11 ,12 ] 等传统真时延单元对硅片的大面积占用,并随着天线阵规模的增大无法满足延时范围的要求,有源滤波器利用晶体管跨导特性代替了传统的LC网络,杜绝了大面积电感,从而获得了较小的尺寸;另一方面,有源滤波器的可调性好,可以进行高精度延时、增益控制,并且可通过级联等方式增加最大延时,如Gm⁃RC全通滤波器、Gm⁃C全通滤波器[13 ,14 ] . ...

... Performance comparison between this paper and other literatures

Table 1 参数 文献[11 ] 文献[12 ] 文献[13 ] 文献[16 ] 本文 工艺 0.18 μm 0.13 μm 0.14 μm 0.13 μm 0.18 μm 带宽(GHz) 0.35~1 1~15 1~2.5 0.96~5.1 0.3~1 延时通道 4 4 4 4 4 输出端口个数 4 1 1 1 4 延时范围(ps) 0~720 0~225 0~550 0~82 0~1030 延时波动 N.A. *14% 2% N.A. 2.4% 增益(dB) 18.5 24 ~12 ~21 25 功耗(mW) 234 555 450 **30.6~52.5 396 面积(mm2 ) 19.995 9.92 1 N.A. 3.8 真时延技术 LC LC Gm⁃C Gm⁃C Gm⁃C

注: *根据所给延时响应估算的值,~每通道增益,**每通道功耗 ...

A 1?to?2.5GHz phased?array IC based on gm?RC all?pass time?delay cells∥2012 IEEE International Solid?State Circuits Conference.

2

2012

... 近年来有源全通滤波器(All Pass Filter,APF)逐渐引起人们的关注.一方面在低GHz级别的工作频带下,相比于传输线以及LC网络[11 ,12 ] 等传统真时延单元对硅片的大面积占用,并随着天线阵规模的增大无法满足延时范围的要求,有源滤波器利用晶体管跨导特性代替了传统的LC网络,杜绝了大面积电感,从而获得了较小的尺寸;另一方面,有源滤波器的可调性好,可以进行高精度延时、增益控制,并且可通过级联等方式增加最大延时,如Gm⁃RC全通滤波器、Gm⁃C全通滤波器[13 ,14 ] . ...

... 晶体管M1,M2,M3,M4实现了一个增益为1的低通信号路径,电阻R1与M4的组合为后级的晶体管提供与输入相同的偏置电压,即V out,DC =V in,DC .另外,NMOS和PMOS管的电流实现了复用,降低了功耗.与传统的Gm⁃RC全通滤波器[14 ] 相比,去除了可变电容的使用,使得面积进一步降低.该延时电路的传输函数和低频下的延时时间为: ...

A 500 kHz~1.4GHz push?pull differential noise cancellation LNA∥2015 IEEE International Conference on Communication Software and Networks.

1

2015

... 采用噪声抵消技术[15 ] 的宽带低噪声放大器,不仅能放大从天线接收的微弱信号,还有改善噪声特性、提高信噪比的作用.本文所设计的差分低噪声放大器如图4 所示. ...

1 GHz 4?element spatially analog IIR?enhanced delay?and?sum beamformer∥2017 IEEE MTT?S International Microwave Symposium

1

5

... Performance comparison between this paper and other literatures

Table 1 参数 文献[11 ] 文献[12 ] 文献[13 ] 文献[16 ] 本文 工艺 0.18 μm 0.13 μm 0.14 μm 0.13 μm 0.18 μm 带宽(GHz) 0.35~1 1~15 1~2.5 0.96~5.1 0.3~1 延时通道 4 4 4 4 4 输出端口个数 4 1 1 1 4 延时范围(ps) 0~720 0~225 0~550 0~82 0~1030 延时波动 N.A. *14% 2% N.A. 2.4% 增益(dB) 18.5 24 ~12 ~21 25 功耗(mW) 234 555 450 **30.6~52.5 396 面积(mm2 ) 19.995 9.92 1 N.A. 3.8 真时延技术 LC LC Gm⁃C Gm⁃C Gm⁃C

注: *根据所给延时响应估算的值,~每通道增益,**每通道功耗 ...