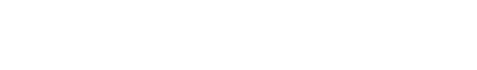

1 卷积神经网络训练算法

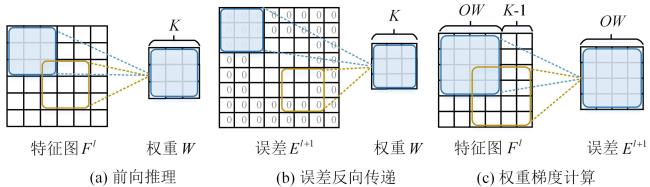

2 加速器设计及优化

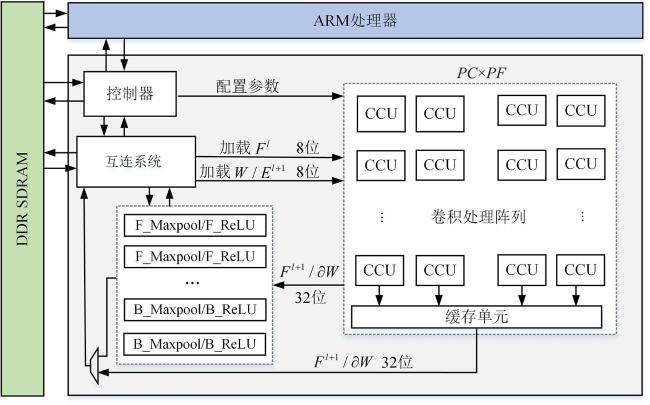

2.1 卷积单引擎架构设计

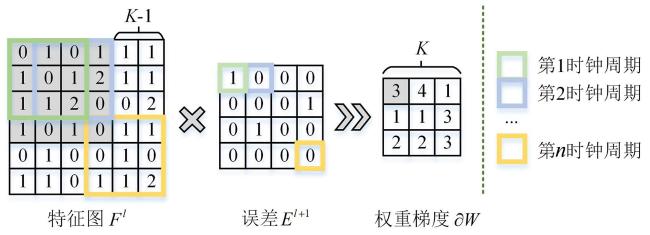

2.2 权重梯度计算优化

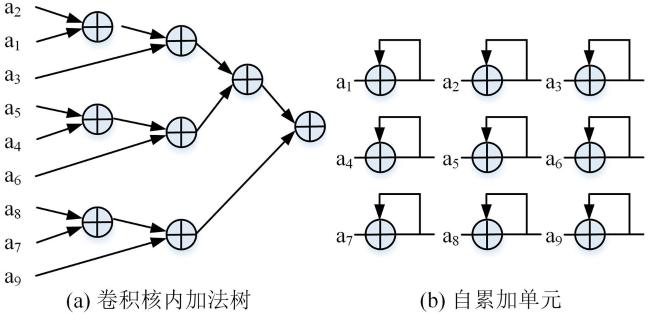

2.3 新型加法树优化

3 实验结果及分析

3.1 实验模型

表1 VGG⁃like网络模型结构Table 1 The structure of VGG⁃like network model |

| 层 | 通道数 | 卷积核数 | 输出高宽 | 卷积核 |

|---|---|---|---|---|

| 卷积1 | 3 | 128 | 32×32 | 3×3 |

| 卷积2 | 128 | 128 | 32×32 | 3×3 |

| 池化 | 128 | 128 | 16×16 | 2×2 |

| 卷积3 | 128 | 256 | 16×16 | 3×3 |

| 卷积4 | 256 | 256 | 16×16 | 3×3 |

| 池化 | 256 | 256 | 8×8 | 2×2 |

| 卷积5 | 256 | 512 | 8×8 | 3×3 |

| 卷积6 | 512 | 512 | 8×8 | 3×3 |

| 池化 | 512 | 512 | 4×4 | 2×2 |

| 全连接 | 8192 | 1024 | - | - |

| 全连接 | 1024 | 10 | - | - |

3.2 资源使用情况

表2 加速器资源使用情况Table 2 Resource usage of accelerators |

| LUT | FF | BRAM | DSP | |

|---|---|---|---|---|

| 总资源数 | 218600 | 437200 | 545 | 900 |

| 占用资源数 | 54725 | 74458 | 134.5 | 615 |

| 使用率 | 25.03% | 17.03% | 24.68% | 68.33% |

3.3 加法树资源使用对比

表3 加法树资源使用对比Table 3 Resource usage of addition trees |

| 优化前 | 优化后 | 优化比例 | |||

|---|---|---|---|---|---|

| 卷积核内加法树 | 自累加单元 | 合计 | |||

3.4 与CPU和GPU平台的对比

表4 CPU,GPU和FPGA的性能比较Table 4 Performance of CPU,GPU and FPGA |

| 参数 | CPU | GPU | FPGA |

|---|---|---|---|

| 平台 | Intel Xeon E5⁃2630 v4 | NVIDIA Tesla K40C | Xilinx Zynq xc7z045 |

| 工艺(nm) | 14 | 28 | 28 |

| 频率(GHz) | 2.2 | 0.745 | 0.2 |

| 精度 | 32位浮点 | 32位浮点 | 8位定点 |

| 每批训练时长(ms) | 539.97 | 13.62 | 57.60 |

| 功耗(W) | 85 | 245 | 3.21 |

| 操作性能(GOPS) | 6.9 | 273.3 | 64.6 |

| 能效(GOPS·W-1) | 0.08 | 1.12 | 20.12 |

3.5 与现有FPGA加速器的对比

表5 不同FPGA训练加速器性能对比Table 5 Performance of different FPGA training accelerators |

| 加速器 | 平台 | 模型 数据集 | 数据 类型 | DSP/LUTs/ FFs/BRAM | 功耗 (W) | 操作性能 (GOPS) | DSP使用效率 (GOPS/DSP) | BRAM使用效率(GOPS/BRAM) | 能效 (GOPS·W-1) |

|---|---|---|---|---|---|---|---|---|---|

| Zhao et al[17] | Altera Stratix V | AlexNet - | 单精度 浮点 | ≈2214/-/ -/- | - | 62.06 | 0.028 | - | - |

| Liu et al[18] | Xilinx ZU19EG | LeNet⁃5 CIFAR⁃10 | 单精度 浮点 | 1500/329.3 k/ 466.0k/174 | 14.24 | 17.96 | 0.012 | 0.10 | 1.26 |

| Fox et al[19] | Zynq ZCU111 | VGG16 CIFAR⁃10 | 8位 定点 | 1037/73.1 k/ 25.6 k/1045 | - | 205 | 0.19 | 0.20 | - |

| Luo et al[20] | UltraScale+ XCVU9P | VGG⁃like CIFAR⁃10 | 8位 定点 | 4202/480 k/ -/≈4717 | 13.5 | 1417 | 0.33 | 0.30 | 104.9 |

| 本文 | ZC706 Xc7z045 | VGG⁃like CIFAR⁃10 | 8位 定点 | 615/54.7 k/ 74.5 k/134.5 | 3.21 | 64.6 | 0.105 | 0.48 | 20.1 |

≈:根据文献中数据转换为本文器件的相应资源. |